This status repeats for every six positive edge transitions of clock signal. The output of rightmost D flip-flop is connected to serial input of left most D flip-flop.Īssume, initial status of the D flip-flops from leftmost to rightmost is $Q_=000$. The 3-bit Ring counter contains only a 3-bit SIPO shift register. The block diagram of 3-bit Ring counter is shown in the following figure. Therefore, Ring counter produces a sequence of states (pattern of zeros and ones) and it repeats for every ‘N’ clock cycles. But, the only difference is that the output of rightmost D flip-flop is given as input of leftmost D flip-flop instead of applying data from outside.

Similarly, ‘N’ bit Ring counter performs the similar operation.

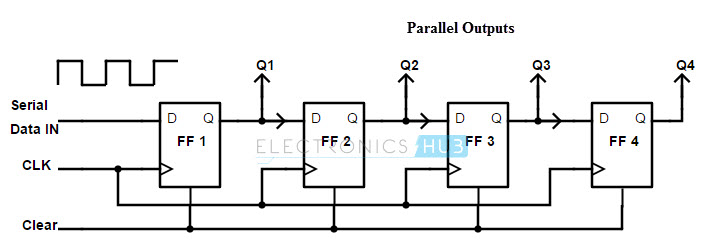

It accepts the data from outside in serial form and it requires ‘N’ clock pulses in order to shift ‘N’ bit data. In previous chapter, we discussed the operation of Serial In - Parallel Out (SIPO) shift register. In this chapter, let us discuss about these two counters one by one. Those are Ring counter and Johnson Ring counter. There are two types of counters based on the type of output from right most D flip-flop is connected to the serial input. Shift registers are also used as counters. Shift register along with some additional gate(s) generate the sequence of zeros and ones. It is utilized at the receiver section before Digital to Analog Converter (DAC) block.

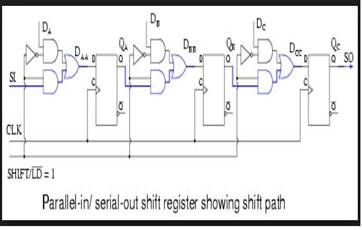

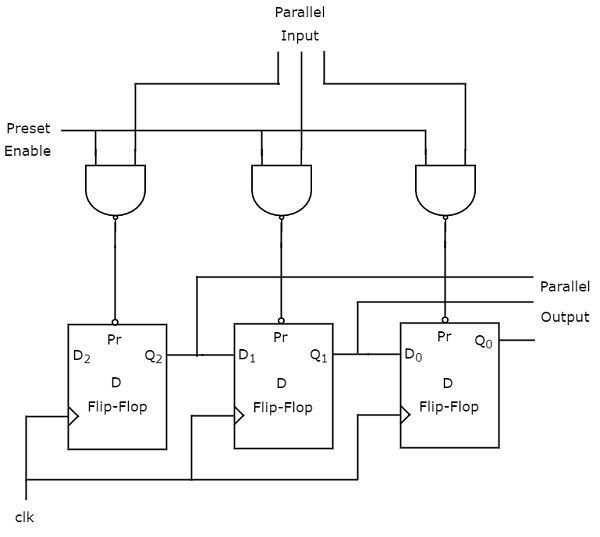

Shift register is used as Serial to parallel converter, which converts the serial data into parallel data. It is utilized at the transmitter section after Analog to Digital Converter (ADC) block. Shift register is used as Parallel to serial converter, which converts the parallel data into serial data. Following are the applications of shift registers. Based on the requirement, we can use one of those shift registers. In previous chapter, we discussed four types of shift registers.

0 kommentar(er)

0 kommentar(er)